SiC 功率器件在散热方面具有更高的要求。SiC 器件可以工作在更高的温度下,在相同功率等级下,其功率模块较 Si 功率模块在体积上大幅降低,因此对散热的要求就更高。如果工作时的温度过高,不但会引起器件性能的下降,还会因为不同封装材料的热膨胀系数(CTE)失配以及界面处存在的热应力带来可靠性问题。

传统的硅基功率模块工作温度一般低于 175 ℃,而碳化硅功率模块会工作在更高的温度下和更大的电场下,因此对封装材料在热电可靠性方面提出了更高的要求。

键合引线材料

尽管无引线键合可以有效地降低功率模块的寄生电感,但引线键合作为一种工艺成熟、低成本的互连技术仍广泛应用于功率模块封装以及 TO 系列分立器件封装中。

互联材料一览

互联材料一览

近年来,随着功率器件封装要求的提高,引线键合材料也得到了新的发展,如大功率器件上的铝带键合技术实现了对铝线键合技术的替代。

其实“丝”和“带”是两种常见并且有鲜明特点的键合材料,比较容易选择,个人认为键合带具有更大的优势。

·可分散芯片表面的键合压力,最大程度保护芯片不受损伤;

如果模块走线基本都是简单的直线型;芯片的有效键合面积内有足够区域可以绑定键合带;单颗芯片使用键合铝带总的载流值大于所使用键合丝的最大根数的载流值,可以尝试使用铝带。

铜材料由于其导电导热性能均优于铝材料,且与硅材料的热膨胀系数失配小于铝与硅材料,因此铜替代铝是封装互连发展的趋势,但是铜替代铝又存在着材料价格高,生产设备升级等成本因素,因此在现阶段用于引线键合的铝铜复合引线或铝铜复合带(Ribbon)材料得以发展,实现了封装互连材料的一种过渡。

纯铜键合材料可以说是在键合丝和键合带中的“战斗鸡”。

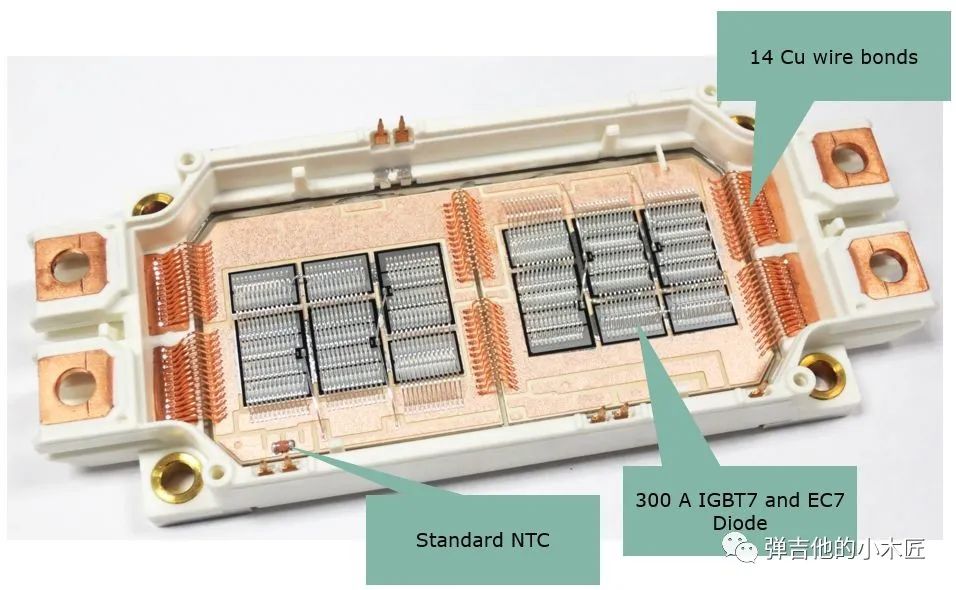

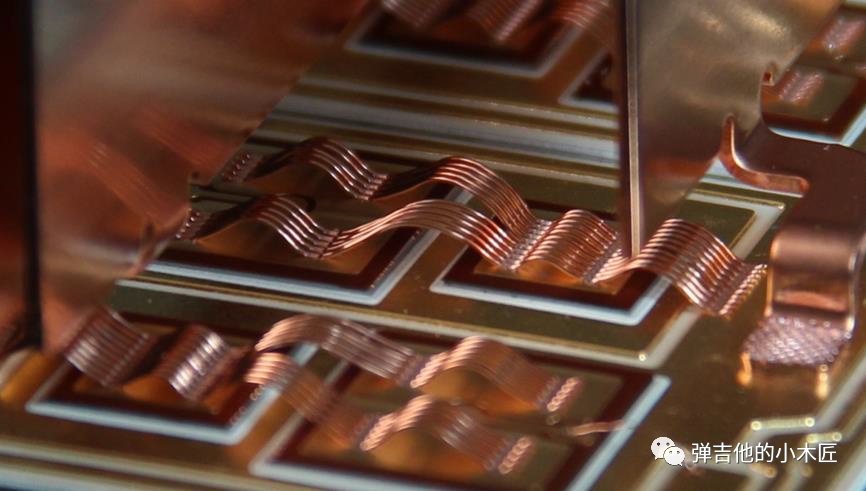

性能优势大家有目共睹,键合铜丝在DBC之间的互联应用也非常多,例如英飞凌工业模块已经在IGBT模块中有大量应用。

英飞凌工业半导体,第7代IGBT,FF900R12ME7_B11模块

但是纯铜键合丝在芯片上的互联技术还是有挑战,因为铜丝硬度较高,芯片表面大多为电镀铝、金和银等材料强度不足以承受铜丝的超声功率及压力,所以想要实现铜丝在芯片表面直接互联,芯片表面需要有一层足够硬的金属层。

如英飞凌的.XT技术,在芯片表面镀铜,使芯片表面具有坚硬的表面。

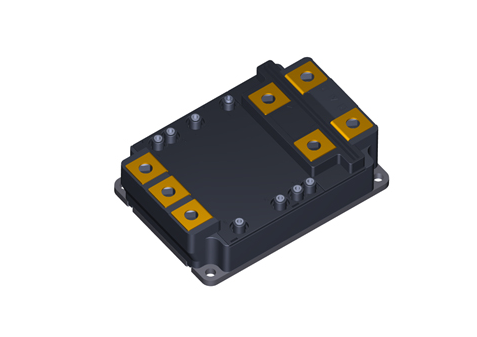

英飞凌工业半导体,.XT技术模块

芯片焊接材料

目前的焊接材料多用锡/铅基的软焊料,这种焊料存在以下缺点:

一是焊料在工艺过程中容易与铜互连材料形成金属间化合物,形成化合物后脆性变大,容易发生断裂等可靠性问题;

二是锡/铅基的软焊料的熔点较低,限制了碳化硅功率器件的应用范围;

使用银、铜等的微米纳米金属颗粒制备的焊膏取代锡/铅基软焊料,利用微米纳米颗粒的尺寸效应,可以在较低的温度下进行烧结,烧结后成为熔点很高的金属块材,而且具备良好的导电导热性能,可以较好地解决上述问题。

SiC基片比硅基片更小更薄。将SiC基片与烧结银(作为基片与框架的连接处)结合使用时,却能拥有SiC基片的优势。这些优势包括更高的开关速度和更高的效率,从而带来更高的热密度,进而得到更小的最终产品。

如果不考虑成本问题,采用银烧结是SIC模块很好的解决方案,例如东芝本月初发布了用于碳化硅(SiC)功率模块的封装技术,宣城能够使产品的可靠性提升一倍,同时减少 20% 的封装尺寸的

iXPLV产品,就是采用了银烧结的解决方案!

除烧结银外,铜焊膏因其与主要互连材料材质相同,并且具有良好的热、电性能,与银焊膏相比,具有更低的价格和更好的抗电迁移性能,近年来也逐步成为研究热点,尤其是采用纳米铜颗粒作为介质实现铜-铜直接互连,在电子封装互连领域具备极大的潜力。

碳化硅在电力电子领域的应用前景一片光明,封装这些“难念的经”,终究都会被克服,产业继续向前发展!

互联材料一览

当前暂无评论,小编等你评论哦!

当前暂无评论,小编等你评论哦!

![ANSYS/ABAQUS使用(带孔平板拉伸实例)[初识有限元CAE分析]](https://img.jishulink.com/cimage/0c683776c596fd2f7dde46fd773a666b_cdn.jpg?image_process=resize,fw_576,fh_320,)